- XJTAG Insights

- Posts

- We Found A Resistive Short On A Prototype

We Found A Resistive Short On A Prototype

Welcome reader!

Here at XJTAG, we use our products internally on our own products and development projects partly to make sure that we’re focussed on their usability and how they’re used in real world applications, but also because we find the testing they perform extremely useful! Recently, one of our prototype boards failed its connection test and we thought this would be the perfect opportunity to show you a real world example of what can go wrong, and how we investigated the problem using the tools that we produce.

When we ran our standard connection test on the board, the results came back quickly with a fault reported: a short between two nets. XJRunner shows a list of the tests it’s running, and when one of them failed, it was highlighted, as shown in Figure 1:

Figure 1 – The error, as shown in XJRunner

This can be expanded to show the pins on those nets, giving the tester a more detailed impression of what’s gone wrong, as shown in Figure 2.

Figure 2 – The expanded error, as shown in XJRunner

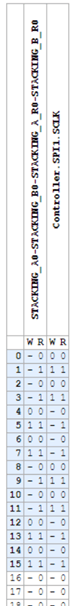

This shows a quick summary of the problem, followed by the details of the two nets in question and all the pins on them. Below that, we can select Error Detail and dive deeper into the test data, seeing the specifics of the test that found the issues. Figure 3 shows some of the relevant tests, highlighting the failed ones in blue. This shows the power of XJTAG’s test patterns – in test 0, the first blue row, we can see that second net, Controller.SPI1.SCLK has been set to 0, as shown in the write column, and has read back that 0 correctly, as shown by the read column. This shows that the pin has been set correctly, and is exactly what we’d expect to see.

The other pin in the first row has been set to tristate, as shown by the dash in the write column, but has also read back a low signal, as shown by the 0 in the read column. This by itself isn’t an automatic fail, however in the next row when Controller.SPI1.SCLK goes high, the STACKING net goes high as well which shows that something has caused this net to change state unexpectedly.

In normal testing, many pins are set simultaneously to speed up the test process, with patterns carefully designed to ensure that any problems will be flagged. Because many pins went from 0 to 1 at this point, we can’t be sure which change caused it, so additional tests will automatically be triggered in XJRunner, allowing it to narrow down the cause of the problem and work out which specific net is causing this one to change. In this example, we can see that the two nets meet at the same device at one end – Figure 1 shows that the first net goes to U1.C10 and the second to U1.D10, strongly implying that the short is likely to be between these two pins. This is, of course, only a suspicion at this point; it’s very likely that this is the location of the short, but further investigation is still required. XJRunner can provide further information to help track the problem down. Selecting the error and then display in Layout Viewer will give a view like the one in Figure 4, showing the path that nets take across the board, making it even more obvious where the nets have pins close together, and hence where a short is likely. |  Figure 3 |

Figure 4 – Layout Viewer

From here, we determined that the cause of the problem was due to ionic contamination from dried flux debris, leading to resistive shorts. Having the boards ultrasonically cleaned an additional time after assembly fixed this issue, and adding this to the process will prevent similar issues from occurring again – the difference this sort of cleaning can make is shown in the example shots from a different board in Figure 5.

Figure 5. Before cleaning |  After cleaning. |

Interestingly, this issue wasn’t a complete short – there was a resistance of about 100 kΩ between the two pins and so using contentious driving to set opposing voltages on the two nets would not have caught the problem, however XJTAG’s test patterns were able to pick up the resistive short. Being able to narrow down the issue to such a small area also allowed us to determine the likely cause of the problem and arrange for the ultrasonic cleaning that fixed it without needing to resort to more expensive options such as x-ray or complete optical analysis.

Testing the board with XJTAG proved extremely useful; not only did it allow us to discover that there was an issue before we started trying to use the board, it also made it extremely easy to find which nets were affected, and from there which pins were the most likely cause of the issue. Doing this manually would have been far more time consuming, especially as the problem pins were hidden under a BGA.

If you would like more information on XJTAG or would like to sign up for a free trial, please get in touch with us here: XJTAG.com/contact

Explore free XJTAG resources

From an Electronics Test Method Finder to Free Trials and Webinars.

Visit the website to see a range of free resources.

Enjoyed this update? Feel free to share with a colleague or friend!